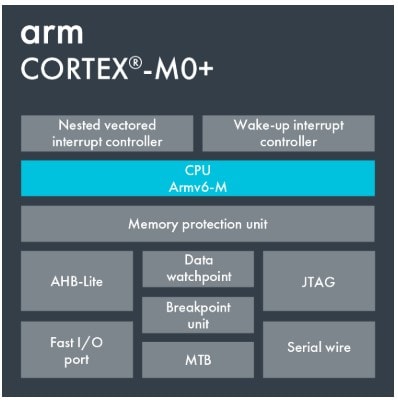

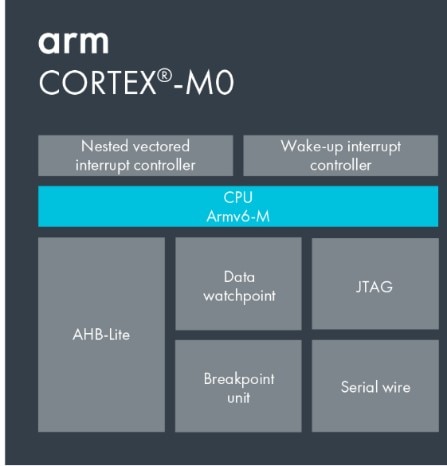

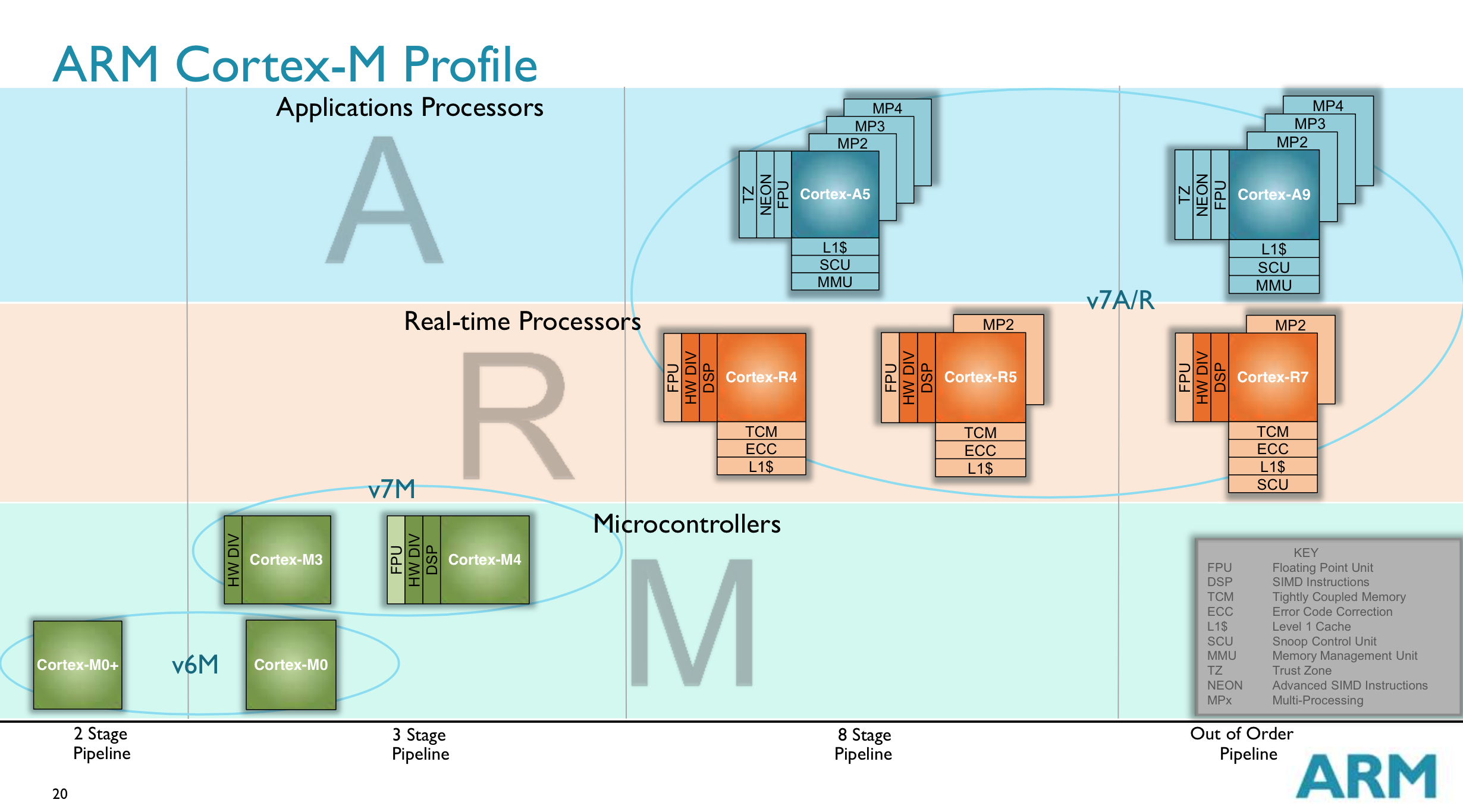

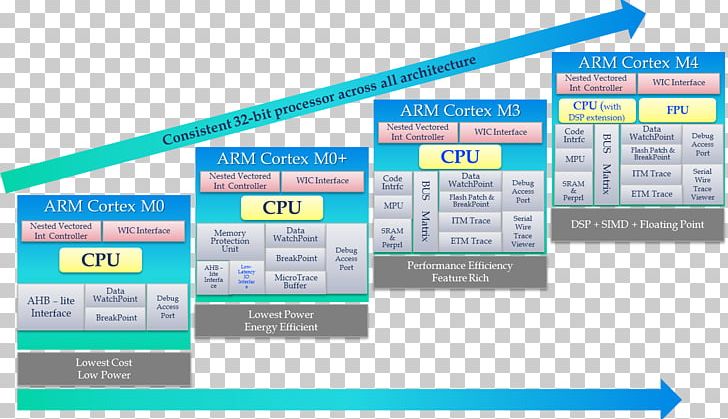

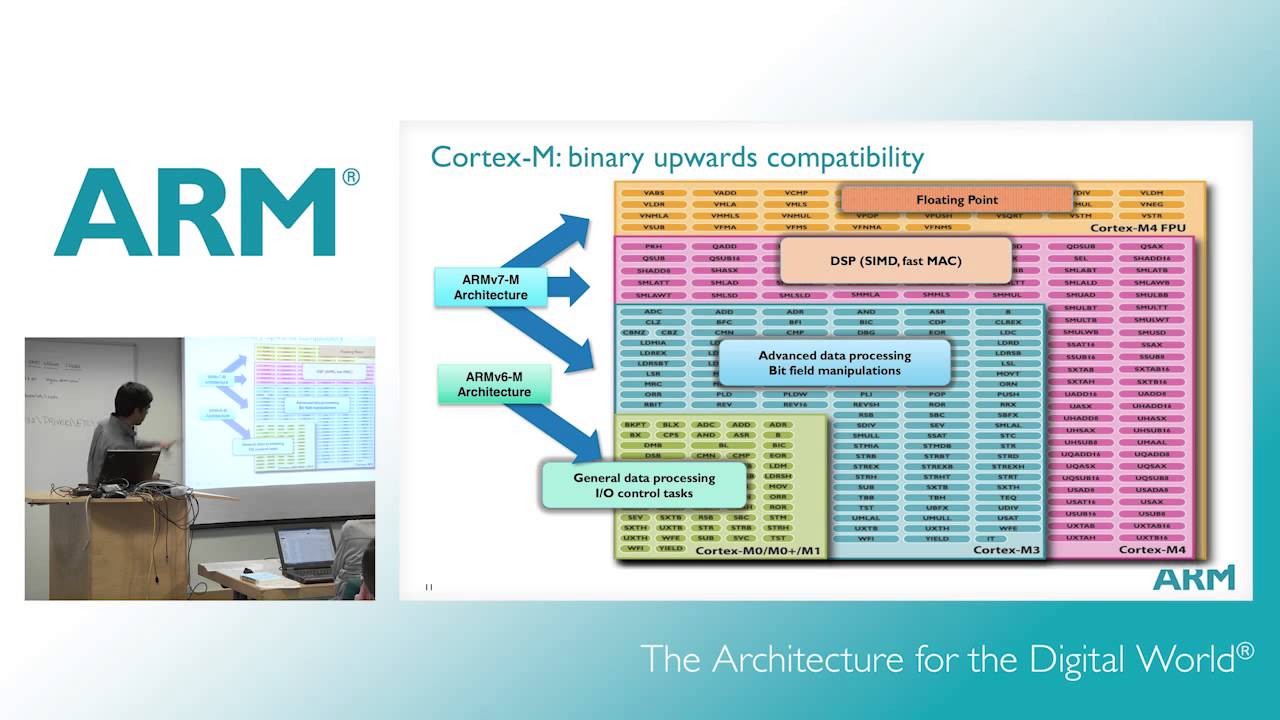

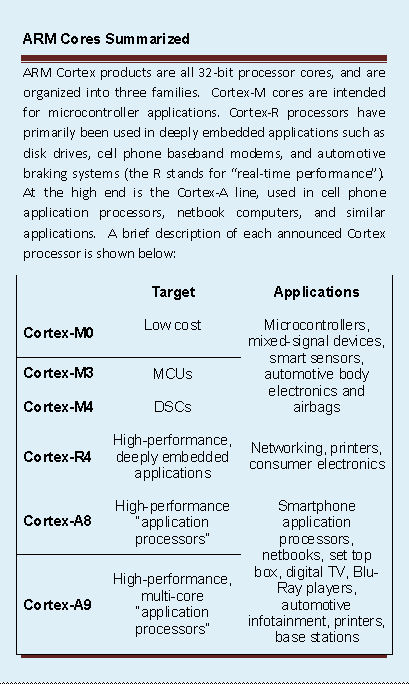

10 What are the features of Cortex M4?12 Why should you design the DSP algorithm in general ARM architecture so that saturation is not required?Low power optimised design ARM v6M Architecture ARM v6M Architecture ARM v6 Architecture ARM v6 Architecture ARM v7M Architecture ARM v7M Architecture ARM CortexM0

Cortex M4 Technical Reference Manual

Cortex m4 processor architecture

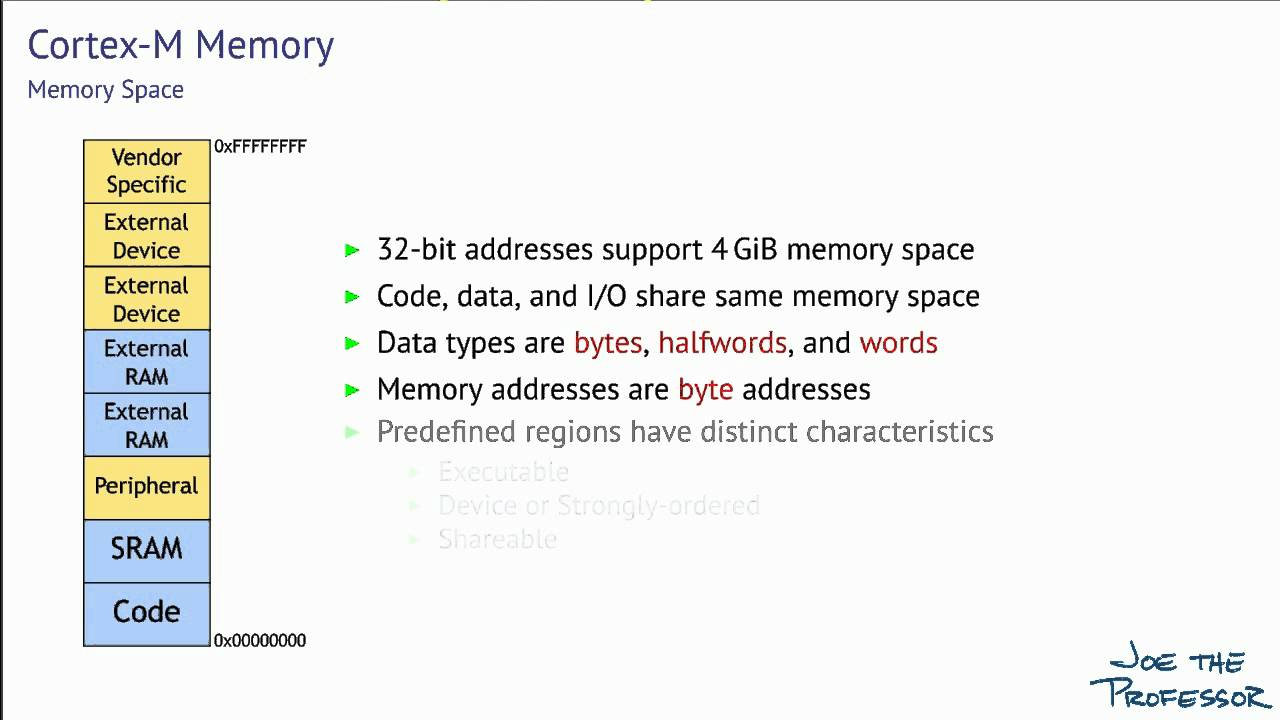

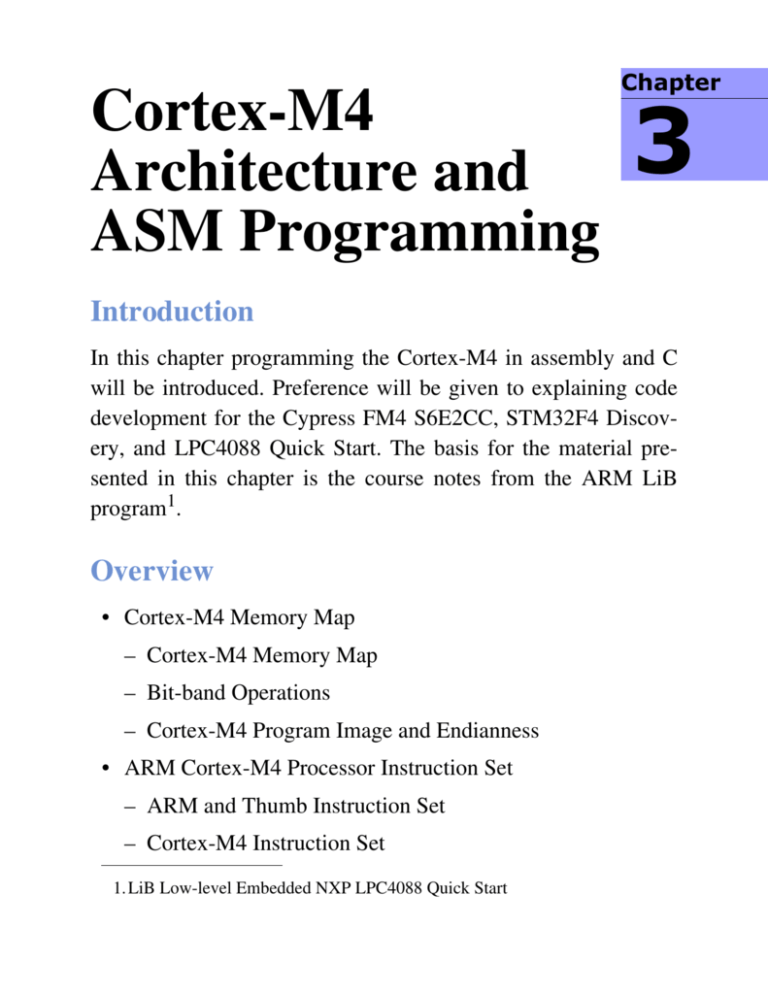

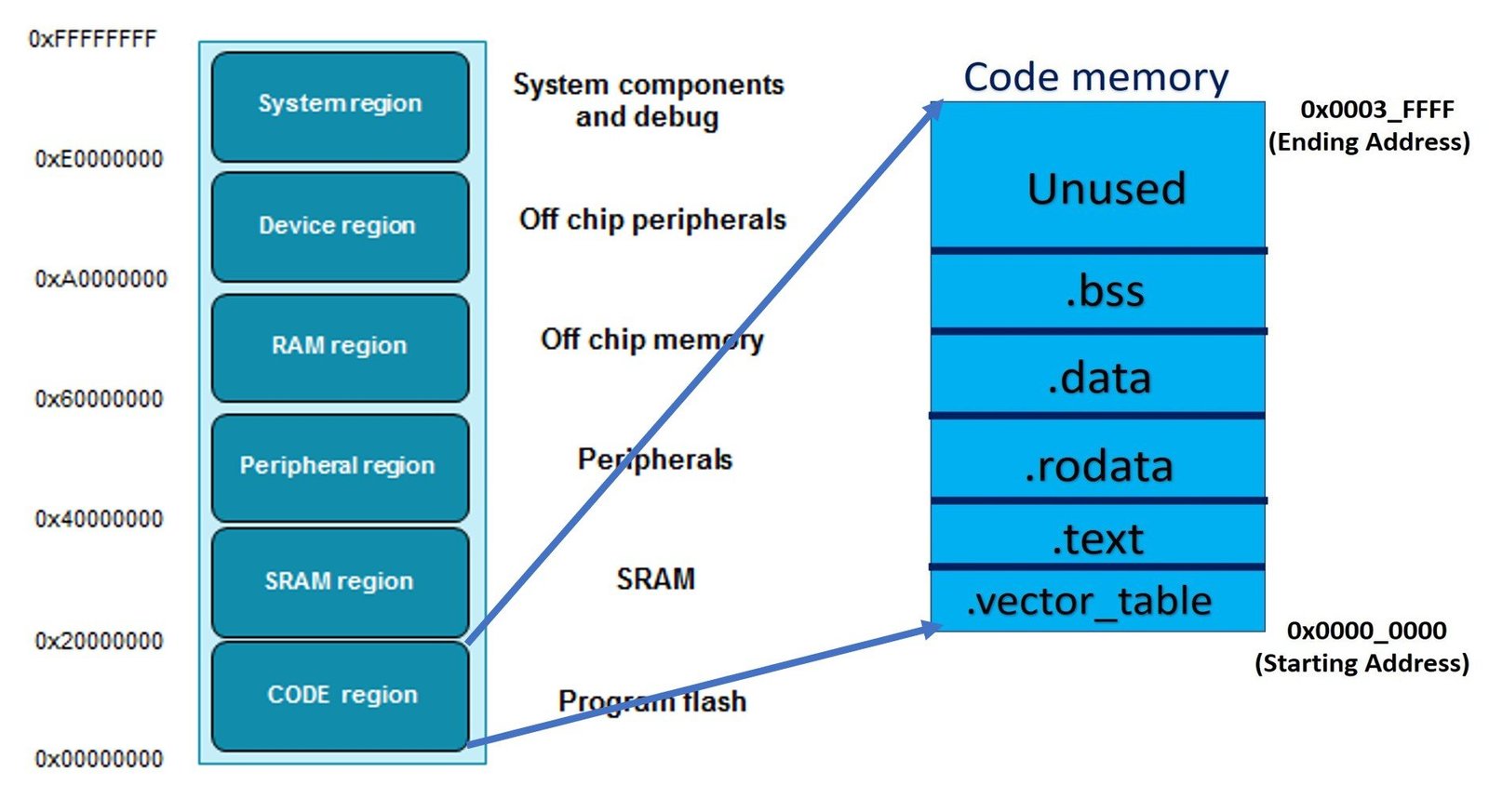

Cortex m4 processor architecture-Chapter 3 • CortexM4 Architecture and ASM Programming 3–2 ECE 5655/4655 RealTime DSP CortexM4 Memory Map † The CortexM4 processor has 4 GB of memory address space – Support for bitband operation (detailed later) † The 4GB memory space is architecturally defined as a number of regions – Each region is given for recommended usageARM® Cortex®M4 serves as a teaching aid for university professors wishing to teach DSP using laboratory experiments, and for students or engineers wishing to study DSP using the inexpensive ARM® Cortex®M4 This book highlights cuttingedge research into emergency early warning management and decisionmaking for severe accidents Using toxic

1

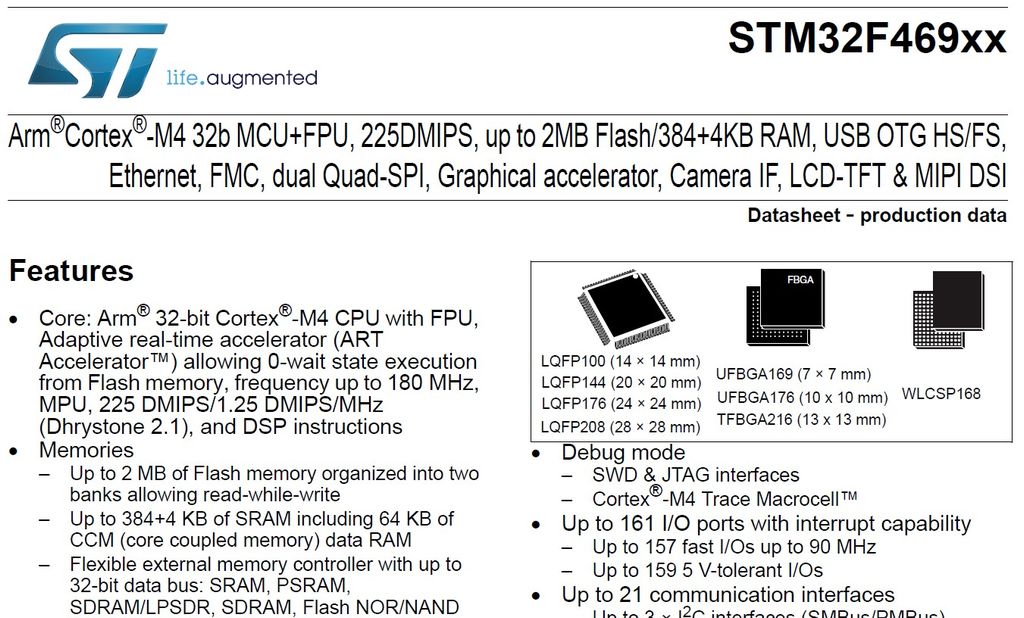

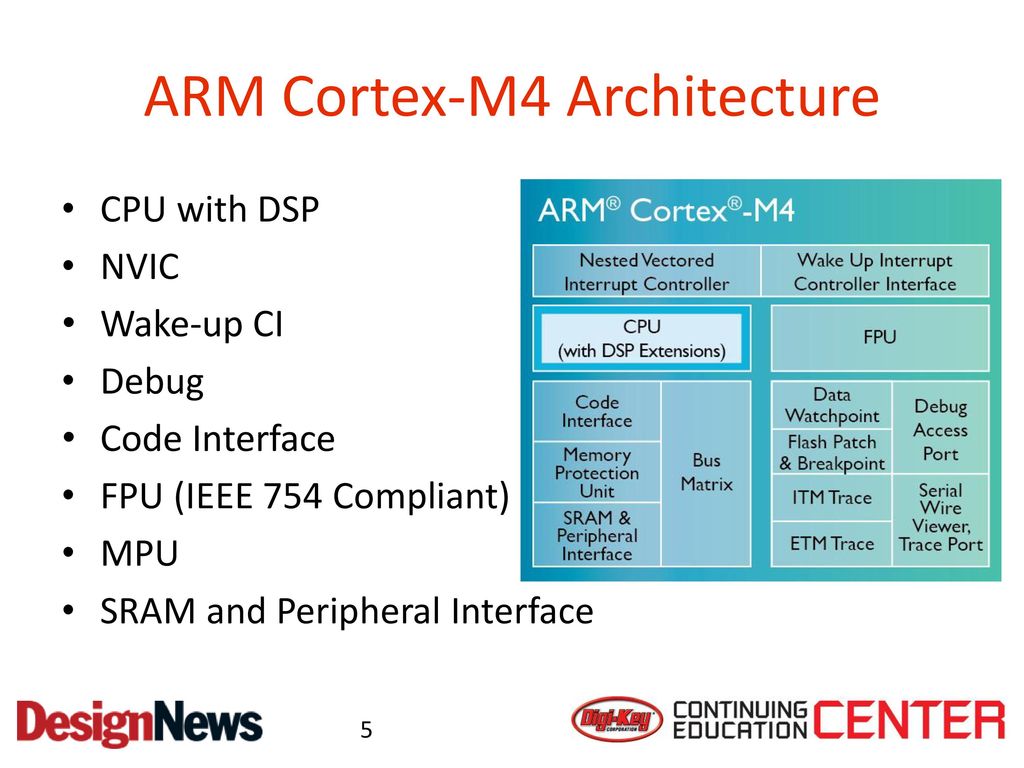

ARM Processor Architecture Embedded Systems with ARM CortextM Updated Monday, ARM Cortex Processors 6 •ARM CortexAfamily 32 bit ARM CortexM4 CPU source ifixitcom 39 A Little About STM32 Embedded Systems Programming on ARM CortexM3/M4 Processor Udemy Free Download With hands on Coding using C Programming and assembly on ARM Cortex M Processor based Microcontroller You will get full coverage of the ARM Cortex M3/M4 processor with full handson lab sessions Once you complete the course, The Arm® Cortex®M4 with FPU processor is the latest generation of Arm® processors for embedded systems It was developed to provide a lowcost platform that meets the needs of MCU implementation, with a reduced pin count and lowpower consumption, while delivering outstanding computational performance and an advanced response to interrupts

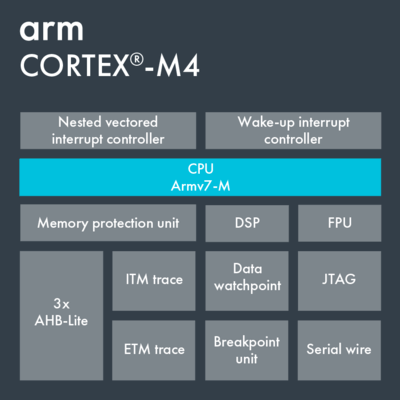

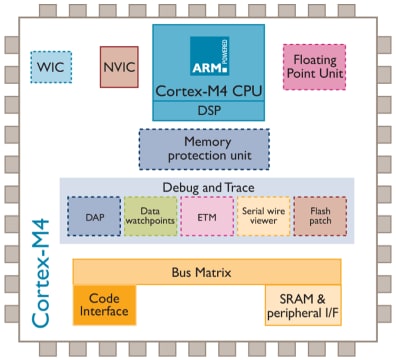

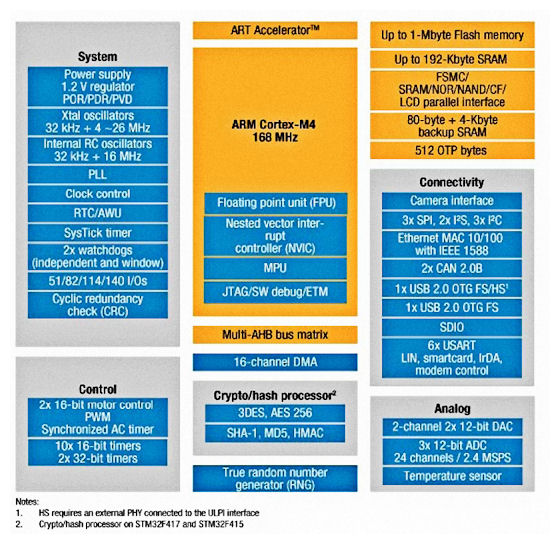

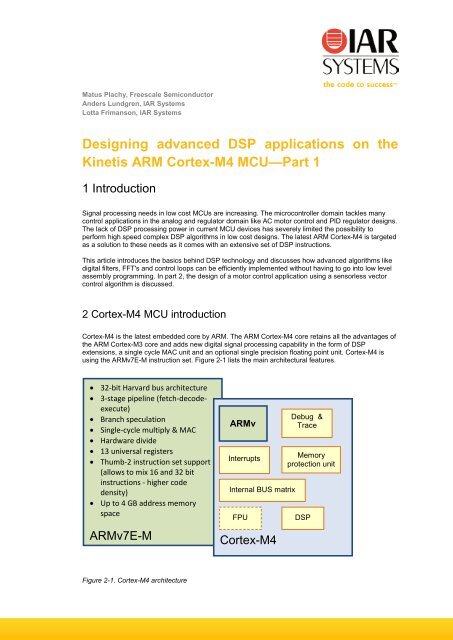

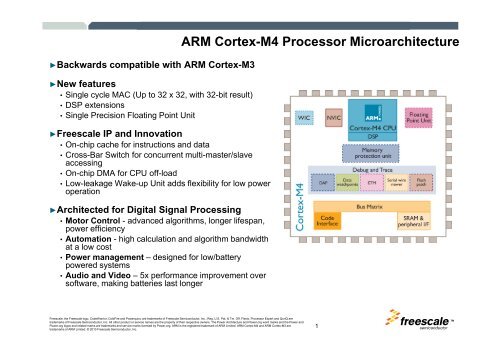

The Arm CortexM4 processor is a highlyefficient embedded processor The CortexM4 processor is developed to address digital signal control markets that demand an efficient, easytouse blend of control and signal processing capabilities The combination of highefficiency signal processing functionality with the lowpower, low cost and easeofuse benefits of the CortexM family ofCortexR processors are used in products that must always meet exacting per\൦ormance requirements and timing deadlines\爀屲The Arm CortexM processor family is a range of scalable, energy efficient, and ea對sy to use processors that meet the needs of tomorrow's smart and connected embedded applicationsCortexM4 support both LittleEndianness and BigEndianness Instructions are always littleendian Loads and stores to Private Peripheral Bus are always littleendian Data Depends on implementation, or from reset configuration ST processors are littleendian

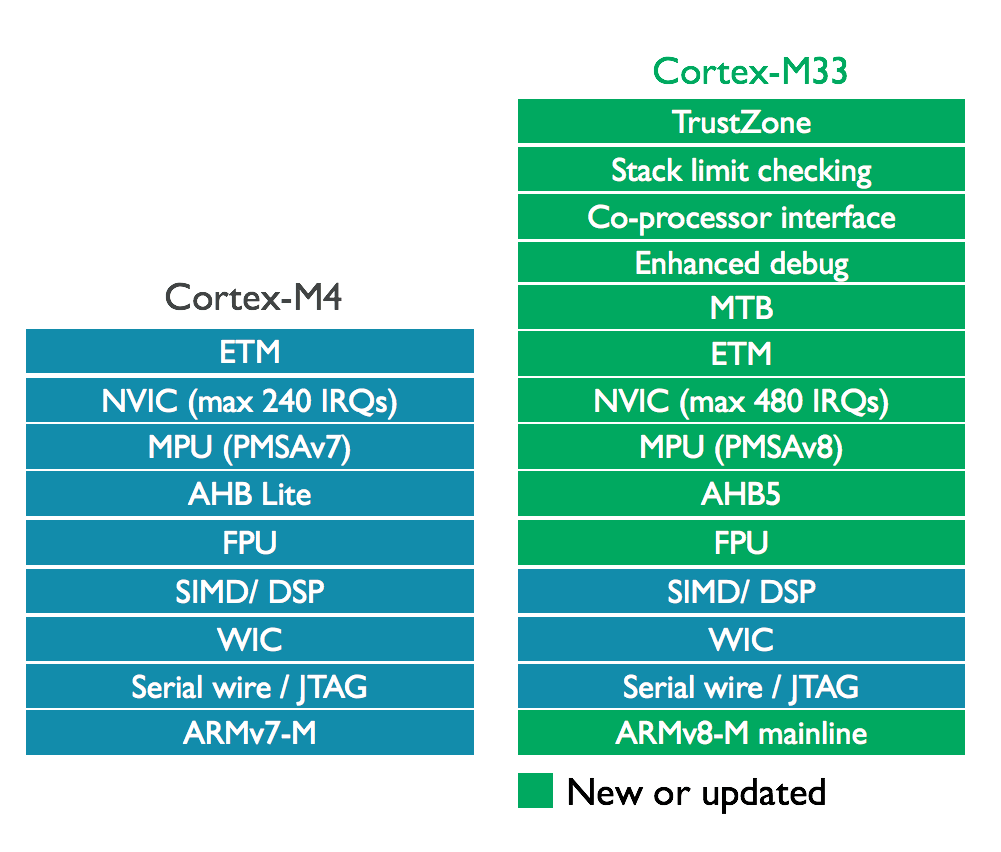

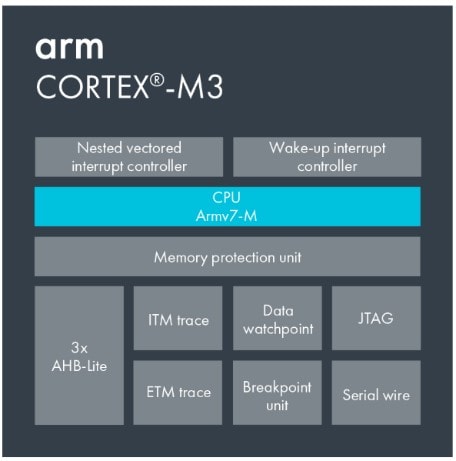

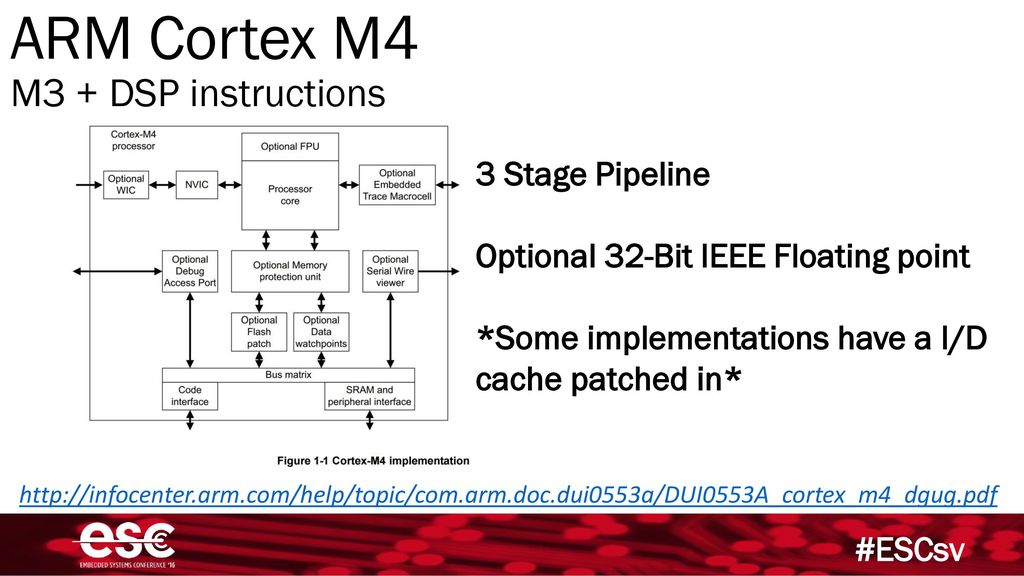

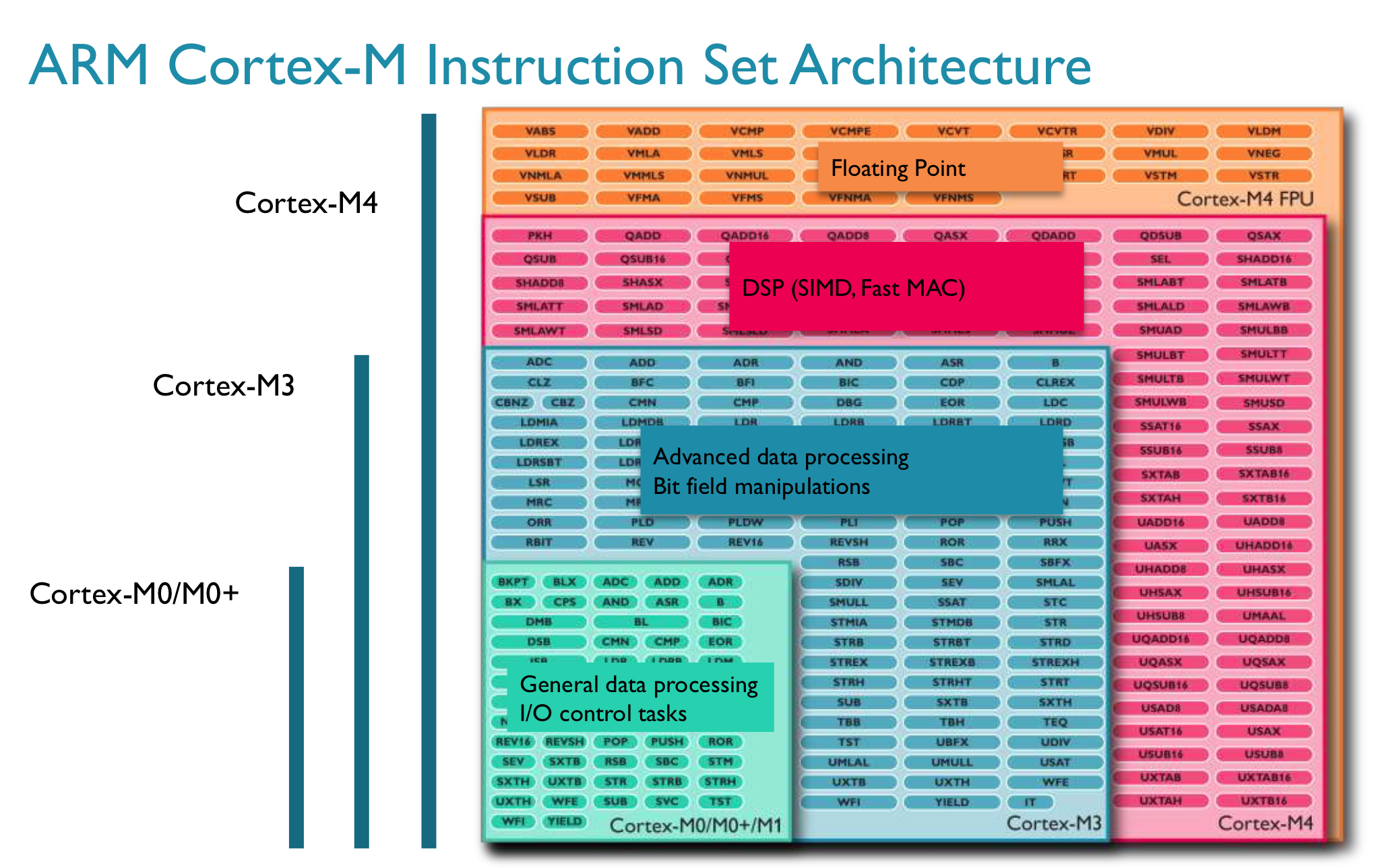

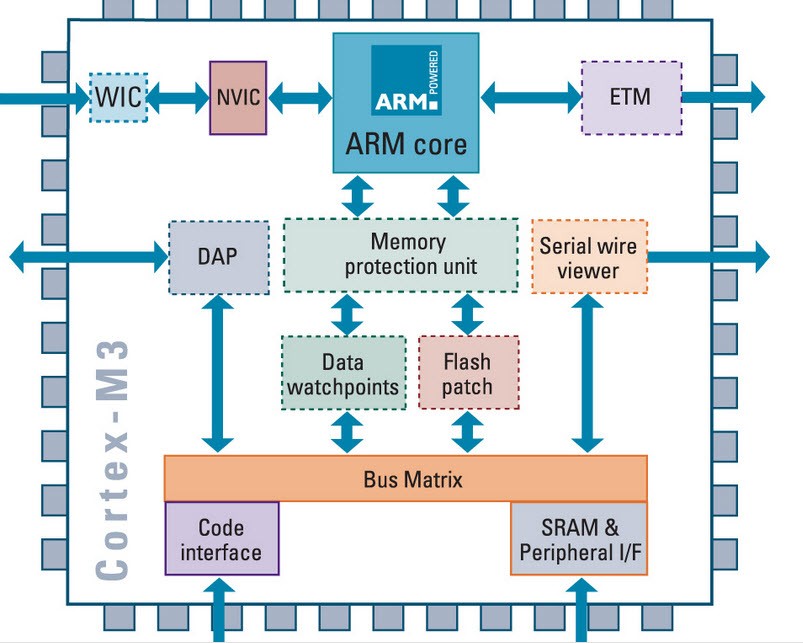

As we will see below, the CortexM3 and CortexM4 are fitted with two trace units which require and extra pin called serial wire out (SWO) Some CortexM3 and CortexM4 devices are fitted with an additional instruction trace unit This is supported by the pin connector and uses an additional four processor pins for the instruction trace pipe Architecture and syntax Generally, it will specify the instruction set syntax There are two slightly different syntaxes are support for ARM and THUMB instructions, divided and unifiedsyntax unified arch armv7em The "arch" instruction used to select the target architecture What the architecture of CortexM4 is ARMv7EMThe CortexM3 and CortexM4 share the same architecture and instruction set (Thumb2) However, the CortexM4 adds a range of saturating and SIMD instructions specifically optimized to handle DSP algorithms For example, consider the case of a 512 point FFT running every 05 second on equivalent offtheshelf CortexM3 and CortexM4 MCUs For

Arm Cortex M4 Microcontrollers Stmicroelectronics

Cortex M Processors And The Internet Of Things Iot

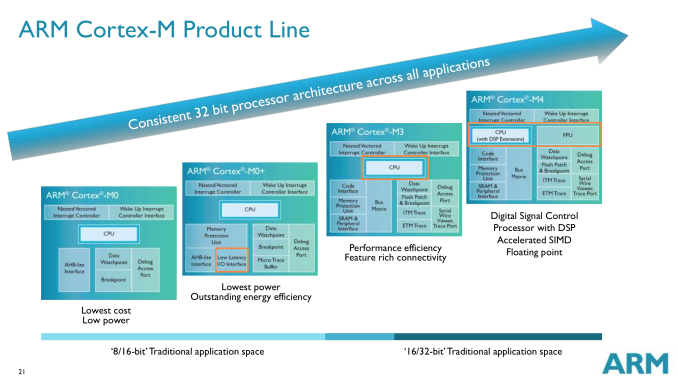

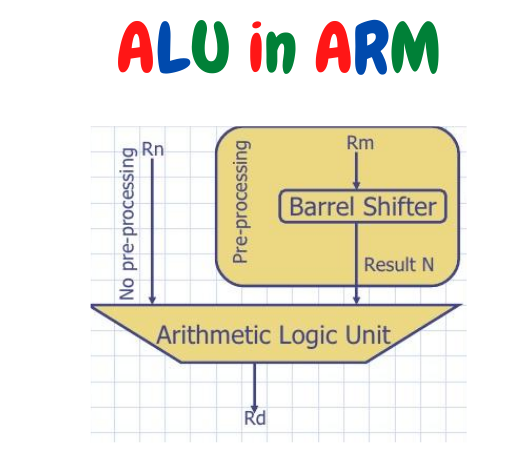

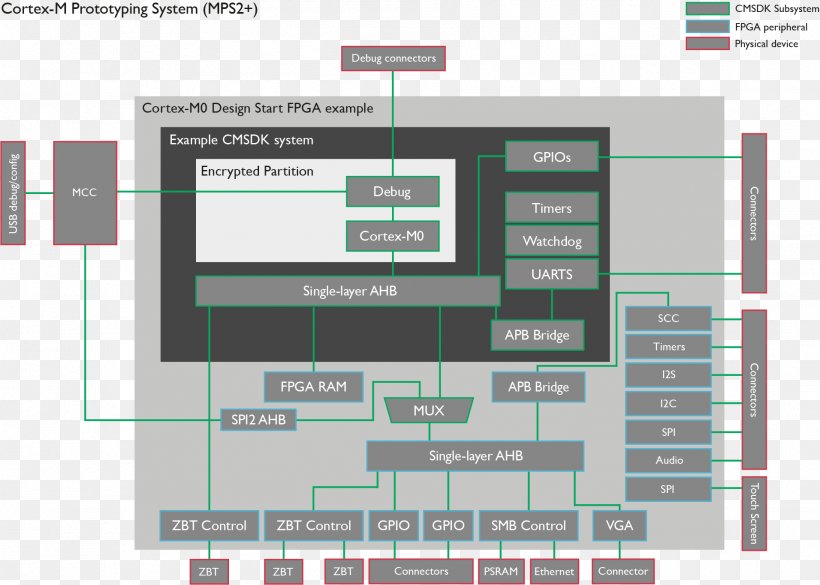

ARM Cortex M Architecture 3 ARM CortexM4 processor Harvard versus von Neumann architecture Different busses for instructions and data • ICode bus Fetch op codes from ROM • System bus Data from RAM and I/O • Dcode bus Debugging • PPB bus Private peripheralsARMv7M architecture memory map, exception model, and thumb2 system;11 ARM CortexM Processors The ARM CortexM processors are high performance, low cost, low power, 32bit RISC processors, designed for microcontroller applications The range includes the CortexM3, CortexM4, CortexM0, Cortex M0, and CortexM1 processors The CortexM1 processor is targeted at implementation in FPGA devices

The Definitive Guide To Arm Cortex M3 And Cortex M4 Processors

Arm Cortex M4 Architecture Microdigisoft Com

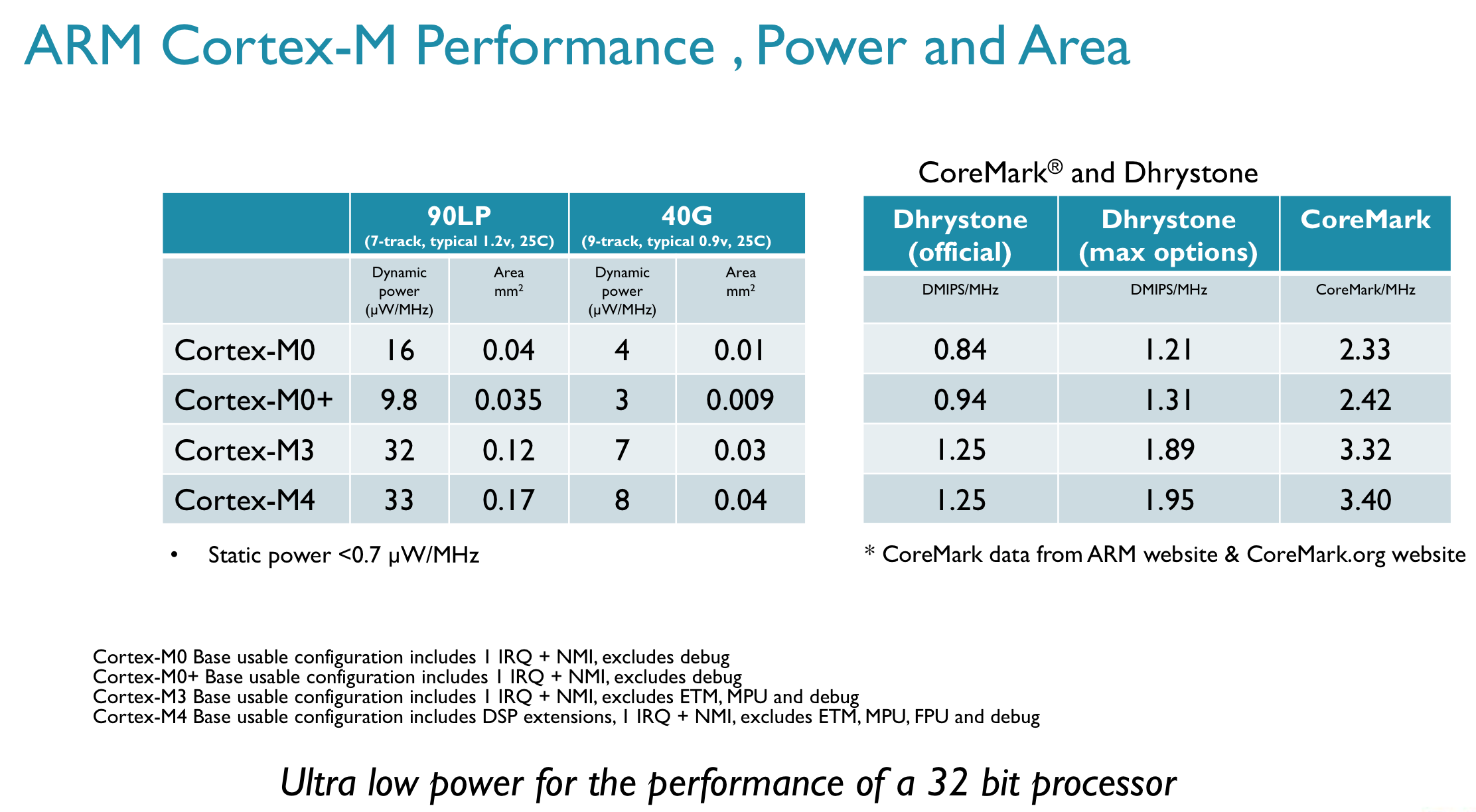

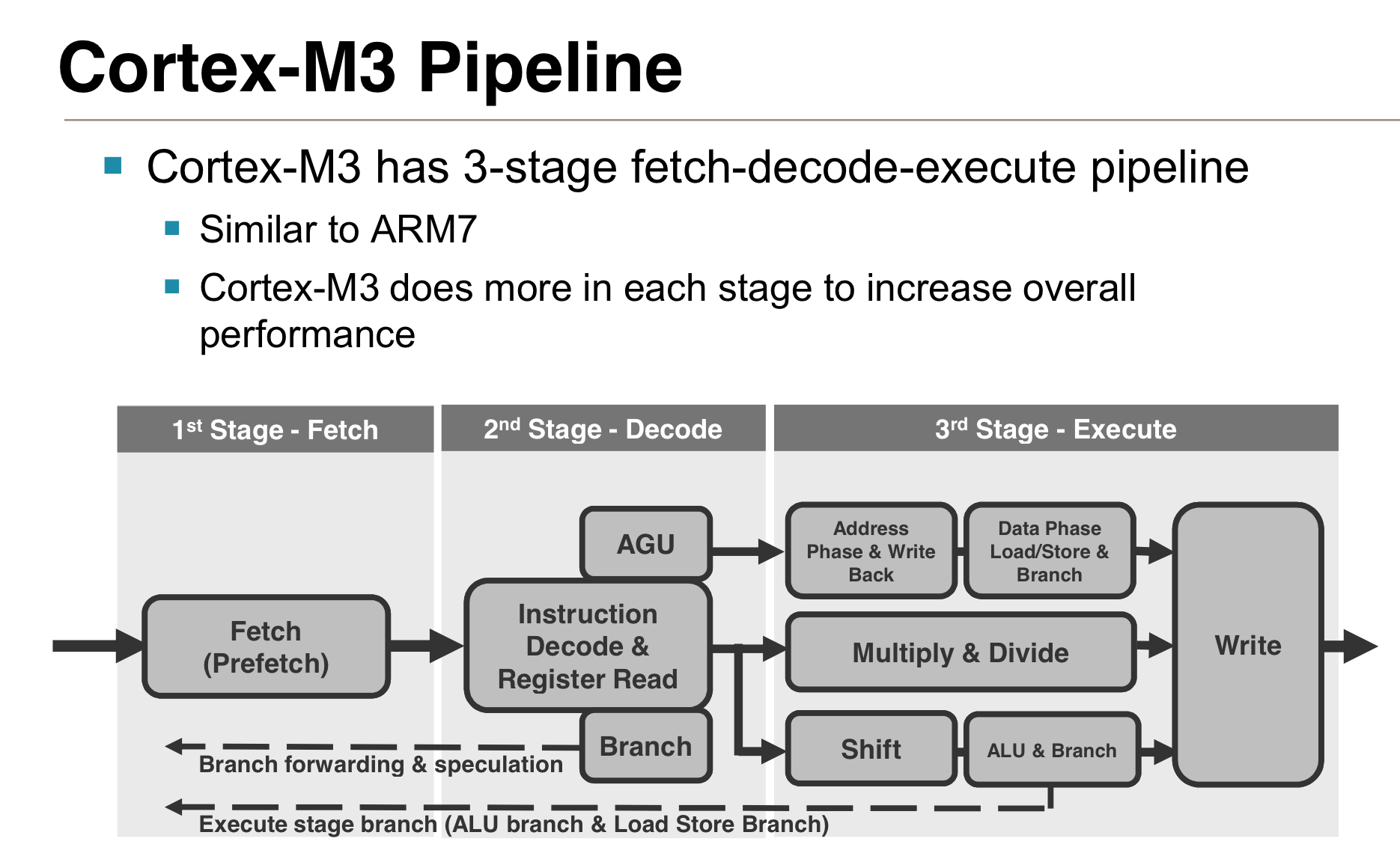

The ARM CorexM4 comes with a number of advantages The processor was developed to address the demands of digital signal control applications The processor offers highefficiency signal processing functionality with lowpower, lowcost, and easeofuse benefits of the CortexM family This recent version of the embedded processor is designedEmbedded ARM Cortex Processors• Cortex M3 The mainstream ARM processor for microcontroller applications High performance and energy efficiency Easy migration path from FPGA to ASIC Advanced3Stage Pipeline Based on ARMv7M architecture 14Conceptually the CortexM4 is a CortexM3 plus DSP instructions, and optional floatingpoint unit (FPU) A core with an FPU is known as CortexM4F Key features of the CortexM4 core are ARMv7EM architecture;

1

Pdf Download The Definitive Guide To Arm Cortex M3 And Cortex M4 Processors Full Free Collection

ARMv7 M 32 ARM Cortex M3 Microcontroller ARMv7E M 32 ARM Cortex M4 Microcontroller ARMv7 R 32 ARM Cortex R4 , ARM Cortex R5 , ARM Cortex R7 Real time ARMv7 A 32 ARM Cortex A5 , ARM Cortex , ARM Cortex A8 , ARM Cortex , ARM Cortex A12 , ARM Cortex A15 , ARM Cortex A17 Krait , Scorpion ,The course, the Cortex M4, will be introduced and explained in terms of hardware, software, and development environments Beginning topics include • ARM Architectures and Processors – What is ARM Architecture – ARM Processor Families – ARM CortexM Series – CortexM4 Processor – ARM Processor vs ARM Architectures † ARM CortexAnswer (1 of 3) The ARMCORTEX M3 and M4 processors are based on Harvard architecture Open up the datasheet of any MCU that runs on ARM CORTEX M3/M4 CPU, for ex STM32F303RE, and in the block diagram section you can notice separate buses for data and instructions But cortex M0 is a vonNeuma

Arm Cortex M4 Microcontrollers Stmicroelectronics

01 Arm Cortex M Instruction Set Architecture Youtube

3 hours ago CMSIS has been designed for the Cortex™M0, CortexM3, and CortexM4 processors and contains name definitions along with helper functions to acc ess View DevelopmentandEvolutionofCerebralandCerebellarCortex the CortexM3 processor is an advanced 3stage pipeline core, based on the Harvard architecture, that incorporates many The existing CortexM processors are based on two architecture versions • CortexM3, CortexM4 and CortexM7 are based on ARMv7M architecture • CortexM0, CortexM0 and CortexM1 are based on ARMv6M architecture The architecture specifications define the behavior of the processors from both software and debug points of viewFigure 11 CortexM4 implementation The CortexM4 processor is built on a highperformance processor core, with a 3stage pipeline Harvard architecture, making it ideal for demanding embedded applications The processor delivers exceptional power efficiency through an efficient instruction set and extensively

1

Are The Arm Cortex Mx Processors Harvard Or Von Neumann Architecture Quora

CortexM4 It provides all the features on the CortexM3, with additional instructions target at Digital Signal Processing (DSP) tasks, such as Single Instruction Multiple Data (SIMD) and faster single cycle MAC operationsThis chapter introduces the CortexM4 processor and its external interfaces Chapter 3 Programmers' Model This chapter describes the CortexM4 processor programmers' model Chapter 4 System Control This chapter provides a summary of the system control registers whose implementation is specific to the CortexM4 processor13 Can you tell about DSP in ARM7TDMI or DSP in STRONGARM or DSP in ARM9E?

Stm32f405rg High Performance Foundation Line Arm Cortex M4 Core With Dsp And Fpu 1 Mbyte Of Flash Memory 168 Mhz Cpu Art Accelerator Stmicroelectronics

Adsp Cm408f Datasheet The Adsp Cm408f Mixed Signal Control Processor Integrates

2 Confidential 3 ARM Architecture profiles §Application profile (ARMv7 A àeg Cortex A8) §Memory management support (MMU) §Highest performance at low power §Influenced by multitasking OS system requirements §TrustZone and JazelleRCT for a safe, extensible system §Realtime profile (ARMv7 R àeg Cortex R4) §Protected memory (MPU) §Low latency and CortexM4 Memory Map • The CortexM4 processor has 4 GB of memory address space– Support for bitband operation (detailed later) • The 4GB memory space is architecturally defined as a number of regions – Each region is given for recommended usage – Easy for software programmer to port between differentdevices Nevertheless, despite of the default memory map,The CortexM3 processor is an advanced 3stage pipeline core, based on the Harvard architecture, that incorporates many new powerful features such as branch speculation, single cycle multiply and hardware divide to deliver an exceptional Dhrystone benchmark performance of 125 DMIPS/MHz

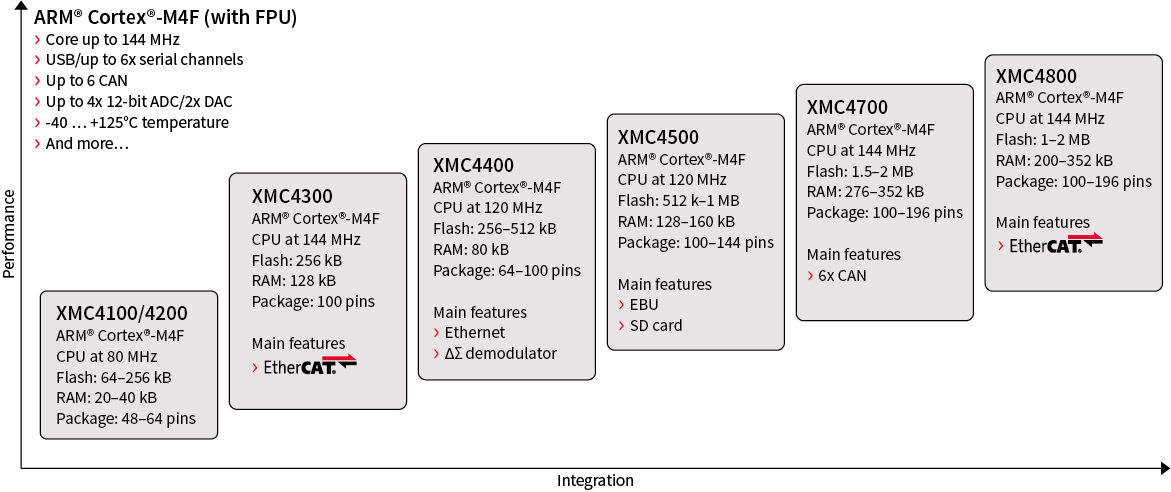

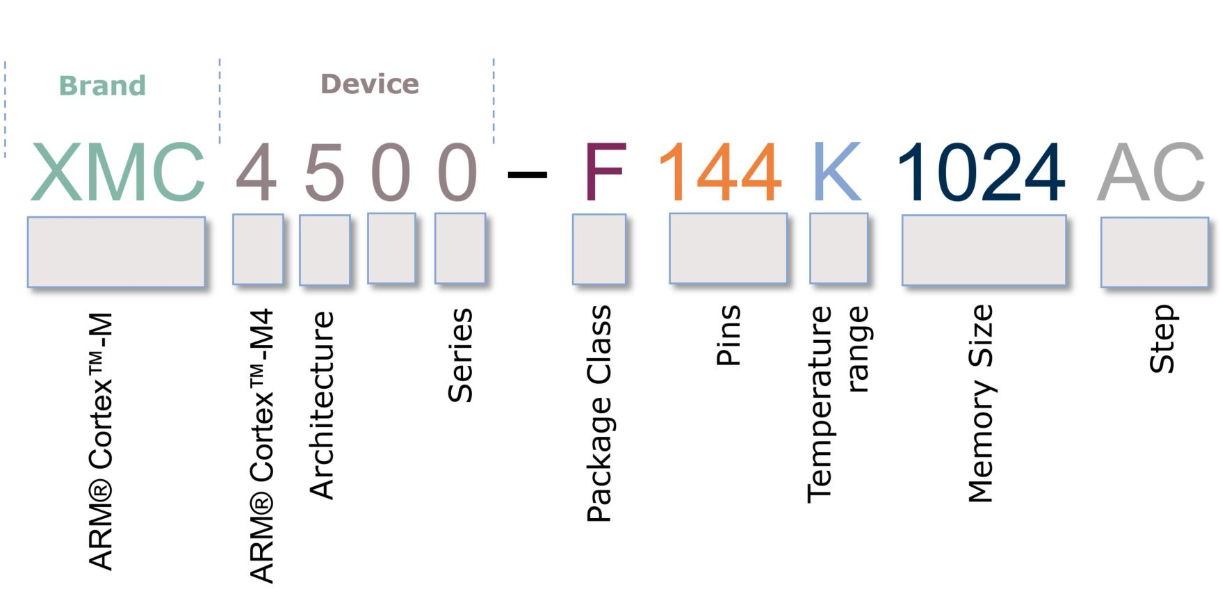

32 Bit Xmc4000 Industrial Microcontroller Arm Cortex M4 Infineon Technologies

2

The Definitive Guide To The Arm Cortex M3 And Cortex M4 Processors Download The Definitive Guide To The Arm Cortex M3 And Cortex M4 Processors PDF/ePub or read online books in Mobi eBooks Click Download or Read Online button to get The Definitive Guide To The Arm Cortex M3 And Cortex M4 Processors book now This site is like a library, Use search box in the widget toThe CortexM4 processor was released in 10 (released products also in 10) The CortexM3 and CortexM4 processors use a 32bit architecture Internal registers in the register bank, the data path, and the bus interfaces are all 32 bits wide The Instruction Set ArchitectureCortexM4 Processor Overview • CortexM4 Processor – Introduced in 10 – Designed with a large variety of highly efficient signal processing features – Features extended singlecycle multiply accumulate instructions, optimized SIMD arithmetic, saturating arithmetic and an

Arm S Cortex M Even Smaller And Lower Power Cpu Cores

Cortex M4 Technical Reference Manual

The CortexM4 processor extends the use of CortexM cores to applications that require more computational performance than available currently with CortexM3 The CortexM4 features a singlecycle multiplyaccumulate (MAC) unit, optimized single instruction multiple data (SIMD) instructions, saturating arithmetic instructions and anCortexM4 Processor Overview with ARM Processors and Architectures 2 University Program Material CortexA8 architecture v7A, with a 13stage pipeline Cortex architecture v7A, with an 8stage pipeline Thumb2 Architecture Profiles 7AApplications 7R RealtimeThe CortexM55 is the first processor built on the Armv81M architecture with Arm Helium technology, a vector processing extension The CortexM55 brings enhanced levels of machine learning and signal processing performance to the next wave of small embedded devices, including wearables, smart speakers, and more Learn more

Cortexfamily

2

The 32bit Arm® Cortex®M4 processor core is the first core of the CortexM line up to feature dedicated Digital Signal Processing (DSP) IP blocks, including an optional FloatingPoint Unit (FPU) It addresses digital signal control applications that require efficient, easytouse control and signal processing capabilities, such as the IoT, motor control, power management, embedded audio,This is especially true for the new ARM CortexM4 processor, which boasts an improved architecture, native digital signal processing (DSP) capabilities and an optional floatingpoint accelerator, which a savvy programmer or hardware engineer can exploit to their adAnd CortexM4 processors, and which enables migration from various processor architectures to the exciting world of the CortexM3 and M4 This book presents the background of the ARM architecture and outlines the features of the processors such as the instruction set, interrupthandling and also demonstrates how to program and utilize the advanced

What Is The Top Level Difference In Features Between Cortex M33 And Cortex M4 Architectures And Processors Forum Support Forums Arm Community

Arm Cortex M0 Silicon Labs

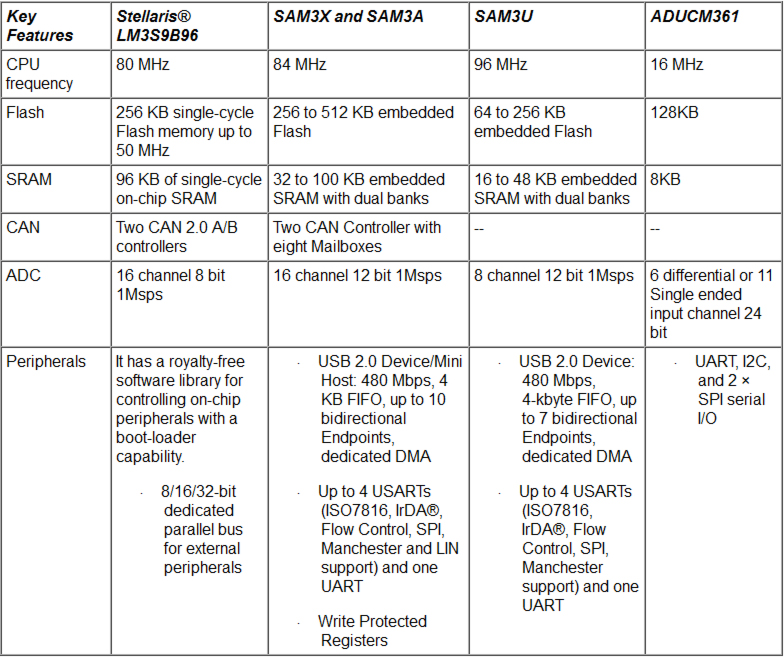

STM32F439NG Highperformance advanced line, Arm CortexM4 core with DSP and FPU, 1 Mbyte of Flash memory, 180 MHz CPU, ART Accelerator, ChromART Accelerator, FMC with SDRAM, TFT, HW crypto STM32F429NG Highperformance and DSP with FPU, ARM CortexM4 MCU with 1 Mbyte Flash, 180 MHz CPU, Art Accelerator, SRAM, TFTARM CortexM4 CPU with FPU at 72MHz !ARM Processor Vs ARM Architectures CortexM0 v6M ARMv6 architecture's thumb instruction set;

Arm Cortex M0 Microcontrollers Stmicroelectronics

1

128KB Flash, KB SRAM11 Tell about the Exception Handling in ARM processor What does the ARM Core do automatically for every exception?The CortexM4 processor is developed to address digital signal control markets that demand an efficient, easytouse blend of control and signal processing capabilities The combination of highefficiency signal processing functionality with the lowpower, low cost and easeofuse benefits of the CortexM family of processors satisfies many markets

32 Bit Xmc4000 Industrial Microcontroller Arm Cortex M4 Infineon Technologies

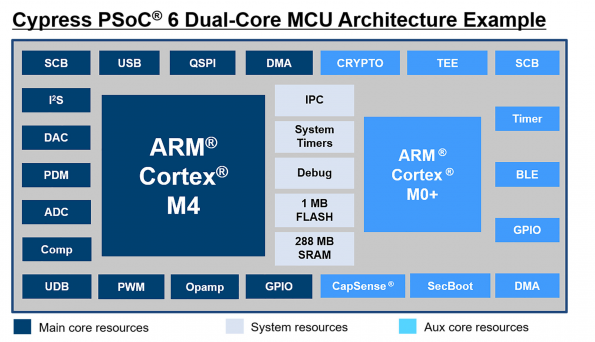

Cortex M4 Architecture And Asm Programming

ARM CortexM4 CPU with FPU at 84MHz 512KB Flash, 96KB SRAM ST Nucleo F103 ST Nucleo L152RE ARM CortexM3 CPU at 32MHz NXP LPC1768 ARM CortexM3 CPU at 96MHz ARM CortexM0 CPU at 48MHz 10 Prototyping Boards used in Performance Tests !PSoC 6 Microcontrollers 32bit Arm® Cortex®M4/M0 The PSoC 6 family is built on an ultralowpower architecture, and the MCUs feature lowpower design techniques to extend battery life up to a full week for battery powered applications The dualcore Arm® Cortex®M4 and CortexM0 architecture lets designers optimize for power and performance simultaneously3stage pipeline with branch speculation Instruction sets Thumb1 (entire) Thumb2 (entire)

Cortexfamily

Arm Cortex M4 Microcontrollers Mouser Costa Rica

Access Free The Definitive Guide To Arm Cortex M3 And Cortex M4 Processors The Definitive Guide To Arm Cortex M3 And Cortex M4 Processors 1 juni 17 is het vijftig jaar geleden dat het iconische, legendarische album Sgt Pepper's Lonely Hearts Club Band verscheen, een plaat die in de ogen van velen de pop en de rockmuziekThe CortexM4 system supports three possible DP implementations Serial Wire JTAG Debug Port (SWJDP) — The SWJDP is a standard CoreSight debug port that combines JTAGDP and Serial Wire Debug Port (SWDP) SWDP — This provides a twopin interface to the AHBAP portCortexM4 processor Using this book This book is organized into the following chapters Chapter 1 Introduction Read this for a description of the componen ts of the processor, and of the product documentation Chapter 2 Functional Description Read this for a description of the functionality of the processor Chapter 3 Programmers Model

Arm Cortex M4 Core And Tiva C Series Peripherals Springerlink

Cortex M4 Part1 Pdf Arm Architecture Instruction Set

Publicly Available Information On The Cortex M4 And Cortex M7 Download Scientific Diagram

Main Stack Pointer An Overview Sciencedirect Topics

Arm Cortex M4 Silicon Labs

Arm Cortex M Wikipedia

1

Arm Cortex M3 Microcontrollers Stmicroelectronics

The Definitive Guide To Arm Cortex M3 And Cortex M4 Processors Amazon Co Uk Joseph Yiu Books

2

Eli Hughes Dsp Development With The Arm Cortex M4 And M7 Cores Eli Hughes Ppt Download

Ingenious Architectural Features Allow St To Extract Maximum Performance From New Microcontroller Family Based On Arm Cortex M4 Cost Less Than 6 Bucks In 1000s Eda360 Insider

Arm S Cortex M Even Smaller And Lower Power Cpu Cores

Arm Cortex M4 Introduction Binh Pham Blog

What Is Arm Processor Arm Architecture And Applications

Arm S Cortex M Even Smaller And Lower Power Cpu Cores

2

Psoc 6 Is Built Around Dual Core Arm Cortex M4 And Cortex M0 At 40nm

Datasheet Review High Performance Stm32 Cortex M4 Microcontroller

Arm S Cortex M Even Smaller And Lower Power Cpu Cores

Arm Cortex M0 Microcontrollers Stmicroelectronics

Designing Advanced Dsp Applications On The Kinetis Arm Cortex

Arm Introduces Cortex M7 Mcu Core For Iot Wearables Industrial And Automotive Applications Cnx Software

2

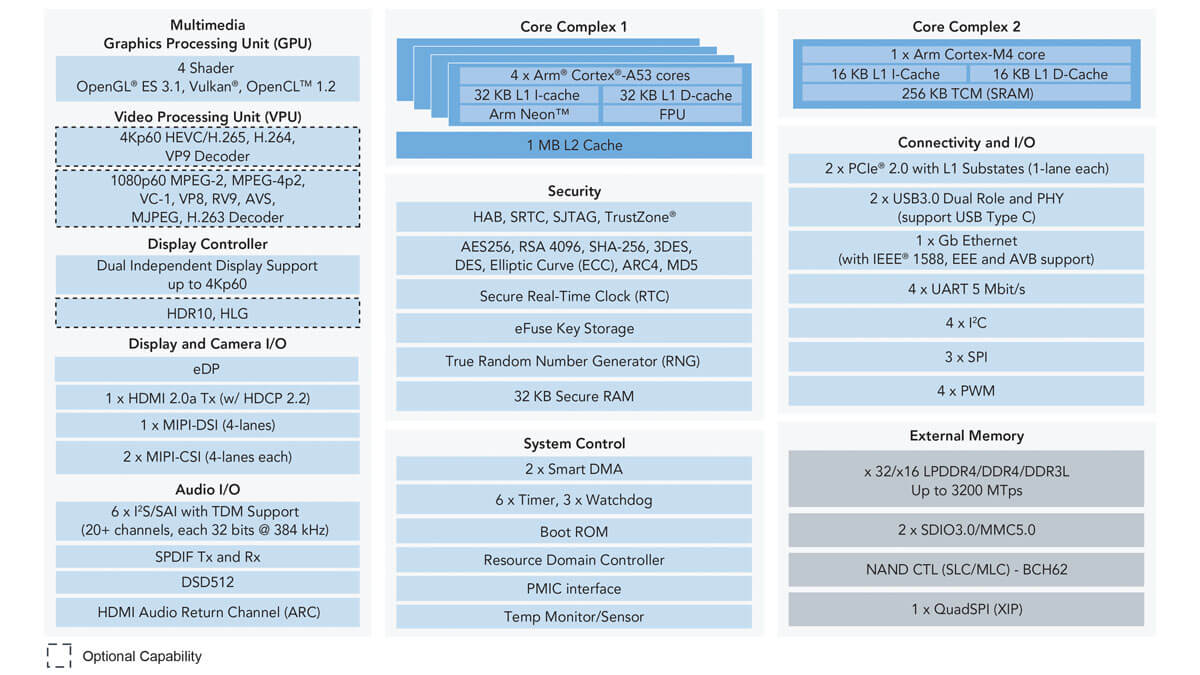

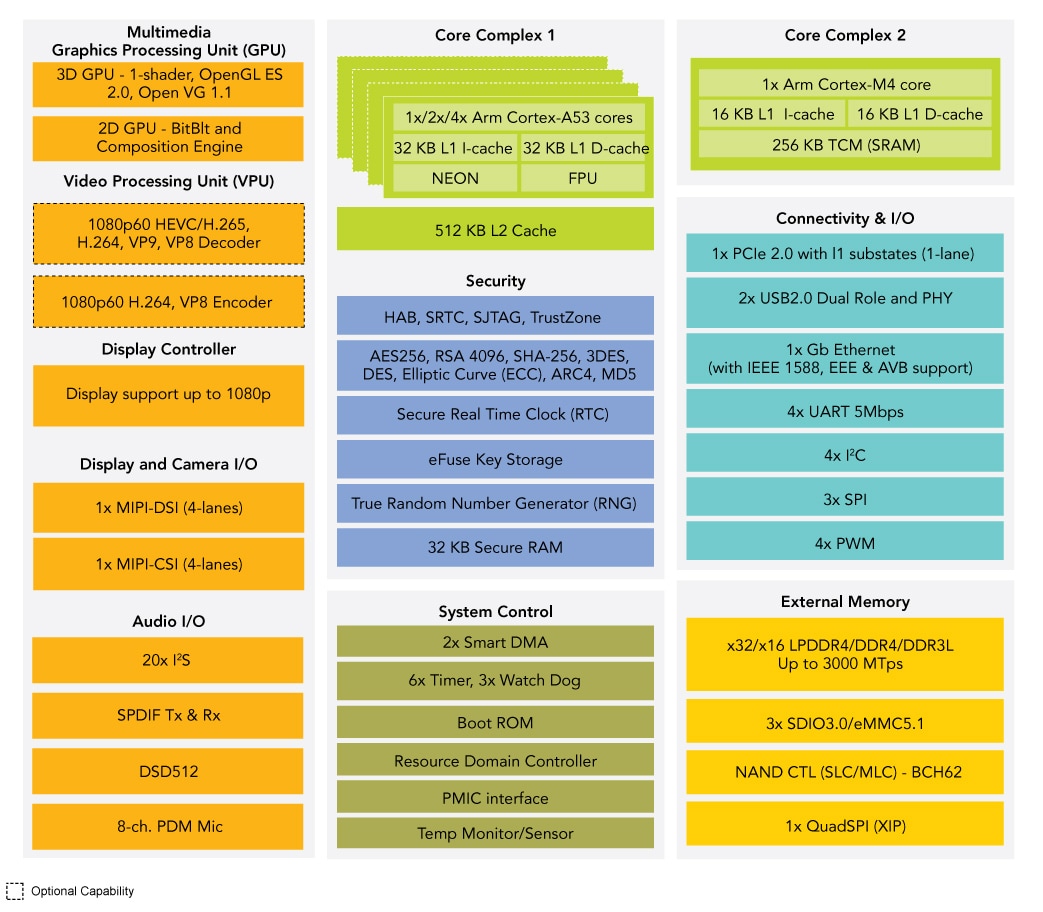

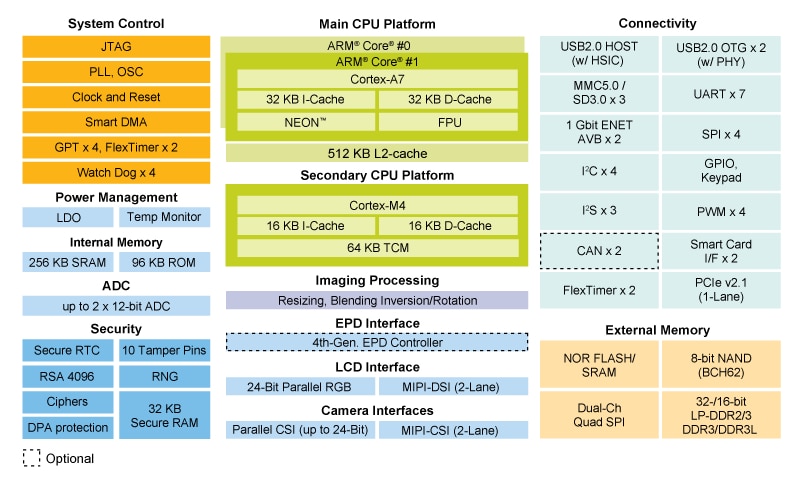

I Mx 8m Applications Processor Arm Cortex A53 Cortex M4 4k Display Resolution Nxp Semiconductors

I Mx 8m Mini Arm Cortex A53 Cortex M4 Nxp Semiconductors

Arm Cortex M4 Architecture Microdigisoft Com

Arm S Cortex M Even Smaller And Lower Power Cpu Cores

Architecture And Implementation Of The Arm Cortex A8 Microprocessor

Arm Cortex M4 Based Mcus Integrate Lcd Controller Offer Spi Flash Interface Edn

Sequence Of Interrupt Processing Steps Arm Cortex M Microcontrollers

Nxp Mixes Cortex M4 M0 In Dual Core Attack Embedded Com

2

The Definitive Guide To Arm Cortex M3 And Cortex M4 Processors Ebook Yiu Joseph Amazon Co Uk Books

The Cortex M3 M4 Embedded Systems Cortex M3 M4 Instruction Sets Ppt Download

Arm Cortex M4 Architecture Microdigisoft Com

What Is Arm Architecture And List Types Of Cortex M Series Ssla Co Uk

Arm Architecture Arm Cortex M Microcontroller Stm32 Instruction Set Architecture Png Clipart Arm Architecture Arm Cortexm

Arm Cortex M3 Silicon Labs

Architecture Features Of Arm Cortex M4 Youtube

Selecting The Perfect Cortex M Based Mcu For Industrial Automation Page 2 Of 2 Electronics For You

Arm Cortex M4 Architecture Microdigisoft Com

Stm32 Wikipedia

Learn The Fundamentals Of Arm Cortex M0 Processor And Designstarttm Hd Youtube

Armv8 M Architecture And Trustzone Security Digikey

Arm Cortex M4 Microcontrollers Stmicroelectronics

Thread Mode An Overview Sciencedirect Topics

Designing With Arm Cortex M4 And A Real Dev Board Ppt Download

Lecture 6 Embedded Hello World Using Arm Cortex M4 Itm And Swo Youtube

Harvard Embedded Architecture Md Github

Nxp Develops Dual Core Ghz Crossover Mcu For Edge Ml Embedded Computing Design

Designing With Arm Cortex M4 And A Real Dev Board Ppt Download

Cortex M4 Technical Reference Manual

Cortex M4 Arm Developer

Block Diagram Of Cortex M3 Processor Architecture Download Scientific Diagram

2

I Mx 7dual Applications Processors Dual Arm Cortex Cortex M4 Nxp Semiconductors

How To Transition From Basic Microcontrollers To Arm Cortex Electrical Engineering Stack Exchange

M7 Processor An Overview Sciencedirect Topics

Arm Cortex M Wikipedia

Stage Pipeline An Overview Sciencedirect Topics

Multi Core Mcu Design With Arm Cortex M Processors And Coresight Soc

Formation Cortex M4 Cortex M4f Implementation Ac6

Stm32 Arm Cortex Mcus 32 Bit Microcontrollers Stmicroelectronics

Arm Cortex M4 Processor Technical Reference Manual Revision R0p1

Which Arm Cortex Cpu Is Right For Your Next Mcu Based Application Digikey

3 Advantages To Using A Multicore Microcontroller Designnews Com

Arm Cortex M4 Processor Microarchitecture

Arm Cortex M4 Arm Architecture Computer Architecture Microprocessor Png 1912x1366px Arm Cortexm Arm Architecture Arm Cortexm4

Arm Cortex M Wikipedia

Arm Technical Tutorial Video Cortex M Series Architectures And Processors Blog Arm Community Blogs Arm Community

Cortex M4 Technical Reference Manual

2

Arm Cortex M Wikipedia

Block Diagram Of Cortex M3 Processor Architecture Download Scientific Diagram

Arm Architecture Wikipedia

Arm Introduces Cortex M4 Core For Digital Signal Controllers Berkeley Design Technology Inc

Arm Cortex M4 Architecture Pdf Document

0 件のコメント:

コメントを投稿